|

|

|

«‘™“ √–∫∫ ◊ËÕ “√·Õπ–≈Õ°

ÀπË«¬∑’Ë 6 ™◊ËÕÀπË«¬ ýø ≈ÁÕ§≈Ÿª ®”π«π 6 §“∫

„∫ß“π∑’Ë 3 ™◊ËÕß“π °“√ —ßý§√“–Àϧ«“¡∂’Ë ®”π«π 3 §“∫

![]()

ýæ◊ËÕ»÷°…“°“√ —ßý§√“–Àϧ«“¡∂’˥ȫ¬ PLL

1.

√È“ßµ—« —ßý§√“–Àϧ«“¡∂’Ë·∫∫ Direct ®“° PLL ‰¥È

2.

√È“ßµ—« —ßý§√“–Àϧ«“¡∂’˥ȫ¬ Presealer ‰¥È

3.

√È“ßµ—« —ßý§√“–Àϧ«“¡∂’Ë‚¥¬„™È¡‘°ý™Õ√ω¥È

1.1

À≈—°°“√∑—Ë«‰ª¢Õß PLL

µËÕ‰ªπ’Èý√“®–°≈Ë“«∂÷ßÀ≈—°°“√ ”§—≠¢Õß√–∫∫ PLL (Phase Locked Loop) ‚¥¬√“¬≈–ýÕ’¬¥π—Èπ “¡“√∂À“ÕË“π‰¥È®“°§ŸË¡◊Õ∑ƒ…Æ’·≈–°“√∑¥≈ÕߢÕß·ºß∑¥≈Õß PLL π’È

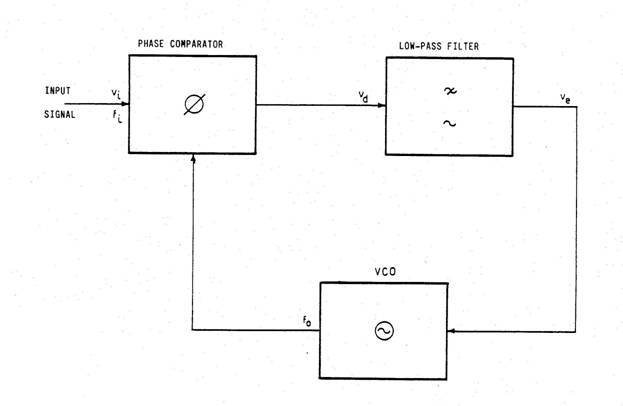

‚¥¬ª°µ‘√–∫∫ PLL ®–ª√–°Õ∫¥È«¬ Ë«π°“√∑”ß“π 3 Ë«π¥—ßπ’È

-

µ—«ýª√’¬∫ý∑’¬∫ýø

-

µ—«°√Õß —≠≠“≥§«“¡∂’˵˔ºË“π

-

¿“§°”ýπ‘¥ —≠≠“≥∑’˧«∫§ÿ¡¥È«¬·√ߥ—π(VCO)

µ—«ýª√’¬∫ý∑’¬∫ýø ®–∑”ÀπÈ“∑’Ëýª√’¬∫ý∑’¬∫§«“¡µË“ßýø √–À«Ë“ß —≠≠“≥Õ‘πæÿµ°—∫ —≠≠“≥∑’ˉ¥È®“°¿“§°”ýπ‘¥ —≠≠“≥∑’˧«∫§ÿ¡¥È«¬·√ߥ—π VCO ýÕ“µÏæÿµ∑’ˉ¥È Vd ®–·∑𧫓¡À¡“¬¢Õߧ˓§«“¡µË“ßýø √–À«Ë“ß —≠≠“≥∑—Èß Õß

·√ߥ—π Vd π’È®–𔉪ºË“πµ—«°√Õß —≠≠“≥§«“¡∂’˵˔ºË“π (À√◊Õ Loop filter) ·≈È«®÷ߪÈÕπ„ÀÈ°—∫¿“§ VCO µËÕ‰ª

—≠≠“≥∑’˪ÈÕπ„ÀÈ°—∫ VCO §◊ÕVe π—Èπ®–∑”„Àȧ«“¡∂’Ë∑’ˉ¥È®“°¿“§ VCO ýª≈’Ë¬π‰ªµ“¡§Ë“¢Õß¡—π π—Ëπ¬ËÕ¡À¡“¬§«“¡«Ë“§«“¡µË“ßýø ¢Õß —≠≠“≥Õ‘πæÿµ°—∫ —≠≠“≥®“°¿“§ VCO ®–¡’§Ë“≈¥πÈÕ¬≈ßý¡◊ËÕ√–∫∫ “¡“√∂

≈ÁÕ°§«“¡§«“¡∂’ˉ¥È ´÷Ëß·√ߥ—π§«∫§ÿ¡®–ý∑Ë“°—∫§Ë“ý©≈’ˬ∑“ߧ«“¡∂’Ë¢Õß —≠≠“≥Õ‘πæÿµ ý¡◊ËÕ√–∫∫‰¡Ë¡’ —≠≠“≥Õ‘πæÿµ ¿“§ VCO ®–°”ýπ‘¥ —≠≠“≥∑’Ë¡’§«“¡∂’˧˓Àπ÷Ëßý√’¬°«Ë“ Free running frequency fo

-234-

1.2

°“√ —ßý§√“–Àϧ«“¡∂’˥ȫ¬ PLL

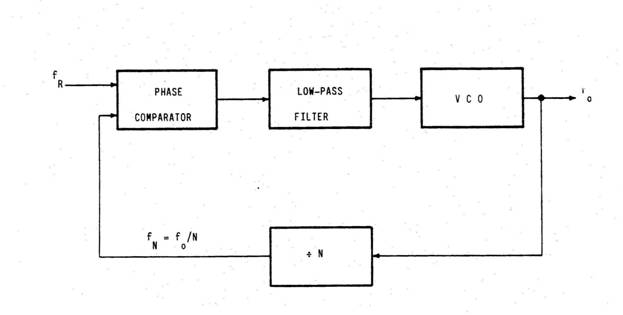

µ—«Õ¬Ë“ß°“√„™Èß“π·∫∫Àπ÷ËߢÕß√–∫∫ PLL §◊Õ°“√ —ßý§√“–Àϧ«“¡∂’Ë „π√–∫∫ Ë«π¡“°∑’Ë„™Èß“ππ—Èπ®–„™È„π°“√ √ȓߧ«“¡∂’ËµË“ß Ê ∑’Ë¡’§Ë“‰¡ËµËÕýπ◊ËÕß

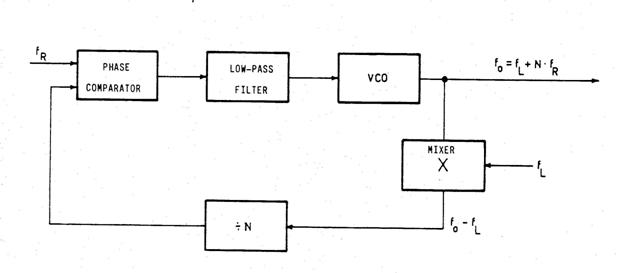

√Ÿª∑’Ë 1.2 · ¥ß√Ÿª·∫∫°“√∑”ß“π¢Õß«ß®√ —ßý§√“–Àϧ«“¡∂’Ë ´÷Ëßý√“ “¡“√∂ √ȓߢ÷Èπ¡“‰¥È‚¥¬„™È«ß®√ PLL ¥È«¬°“√·∑√°µ—«À“√∑’Ë “¡“√∂‚ª√·°√¡§Ë“‰¥È√–À«Ë“ßýÕ“µÏæÿµ¢Õß¿“§ VCO °—∫Õ‘πæÿµ¢Õßµ—«ýª√’¬∫ý∑’¬∫ýø

√Ÿª∑’Ë 1.1 ‰¥Õ–·°√¡¢Õß√–∫∫ PLL

≈—°…≥–ý™Ëππ’È®–∑”„ÀÈ«ß®√ PLL ≈ÁÕ°§«“¡∂’Ë∑’ˉ¥È®“°ýÕ“µÏæÿµ¢Õßµ—«À“√§«“¡∂’Ë fN´÷Ëß®–¡’§Ë“ý∑Ë“°—∫§«“¡∂’Ë

ÕÈ“ßÕ‘ß fR·≈–®–¡’§Ë“¥—ßπ’È

fR

= fN = fo/N

®–‰¥È

fo

= N.fR

-235-

®“° ¡°“√∑’ˉ¥Èý√“ “¡“√∂ √È“ß —≠≠“≥§«“¡∂’Ë fo ∑’Ë¡’§Ë“µ“¡µÈÕß°“√‰¥È ‚¥¬¡’§Ë“ý∑’¬∫°—∫§«“¡∂’Ë fR ∑’Ë∂Ÿ° ý°≈¥È«¬§Ë“¢Õßµ—«À“√ N

ýæ√“–©–π—Èπ«ß®√ —ßý§√“–Àϧ«“¡∂’Ëπ’È®÷ßýªÁπý§√◊ËÕß°”ýπ‘¥ —≠≠“≥·∫∫Àπ÷Ëß ‚¥¬¡’ýÕ“µÏæÿµ∑’Ë¡’§«“¡∂’ËýªÁπ®”π«πý∑Ë“¢Õߧ«“¡∂’ËÕÈ“ßÕ‘ß

∂È“µÈÕß°“√„ÀÈý§√◊ËÕß°”ýπ‘¥ —≠≠“≥§«“¡∂’Ëπ’È¡’§Ë“§«“¡∂Ÿ°µÈÕß·≈–¡’ý ∂’¬√¿“æ¡“°¢÷Èß∑”‰¥È‚¥¬°“√„™È —≠≠“≥§«“¡∂’ËÕÈ“ßÕ‘ß∑’Ë¡’§«“¡∂Ÿ°µÈÕß·≈–¡’ý ∂’¬√¿“æ ýæ√“–©–π—Èπý√“®÷ߧ«√„™Èµ—«°”ýπ‘¥ —≠≠“≥·∫∫§«Õµ´Ïýæ◊ËÕ √È“ß —≠≠“≥§«“¡∂’ËÕÈ“ßÕ‘ß ´÷Ëß®–∑”„ÀÈý√“‰¥Èý§√◊ËÕß°”ýπ‘¥ —≠≠“≥§«“¡∂’Ë∑’Ë¡’§«“¡∂Ÿ°µÈÕß·≈–¡’ý ∂’¬√¿“æ

1.3.1 °“√ —ßý§√“–Àϧ«“¡∂’˥ȫ¬«‘∏’ Direct

√Ÿª∑’Ë 1.3 · ¥ß«ß®√լ˓ßßË“¬∑’Ë ÿ¥¢Õß°“√ —ßý§√“–Àϧ«“¡∂’Ë ´÷Ëߧ«“¡∂’Ëπ—Èπ®–∂Ÿ° √ȓߢ÷Èπ®“°°“√∑”ß“π¢Õߺ≈÷°§«Õµ´Ï ·≈–∂Ÿ°À“√¥È«¬§Ë“ N ´÷Ëß®–∑”„ÀÈý√“‰¥È —≠≠“≥§«“¡∂’Ë∑’˵ÈÕß°“√ fo ý¡◊ËÕý√“ªÈÕ𧫓¡∂’ËÕÈ“ßÕ‘ß

fR ´÷Ëß“®–∑”„Àȧ«“¡∂’Ë∑—Èß Õß¡’§«“¡ —¡æ—π∏Ï¥—ßπ’È

fR

= fo/N

-236-

¥—ßπ—Èπ —≠≠“≥§«“¡∂’ËýÕ“µÏæÿµ∑’ˉ¥È®÷ß¡’§Ë“ýªÁπ°’Ëý∑Ë“¢Õߧ«“¡∂’ËÕÈ“ßՑߥ—ßπ’È

fo

= N.fR

µ—« —ßý§√“–Àϧ«“¡∂’Ë·∫∫π’Èý√“®–ýÀÁπ‰¥È®“°√Ÿª∑’Ë 1.3 ´÷Ëߧ«“¡∂’ËýÕ“µÏæÿµ∑’ˉ¥È®–∂Ÿ°®”°—¥¥È«¬µ—«À“√∑’Ë

‚ª√·°√¡‰¥È

„πª—®®ÿ∫—πæ∫«Ë“ý§√◊ËÕß°”ýπ‘¥ —≠≠“≥§«“¡∂’Ë∑’Ë„™Èµ—«À“√§«“¡∂’Ë∑’Ë‚ª√·°√¡‰¥È “¡“√∂„ÀÈ —≠≠“≥§«“¡∂’Ë

ýÕ“µÏæÿµ‰¥È Ÿß ÿ¥ª√–¡“≥ 10 MHz ´÷ËßýªÁπ§Ë“§«“¡∂’Ë Ÿß ÿ¥ fo

À—«¢ÈÕµËÕ‰ª

-237-

√Ÿª∑’Ë 1.3

√Ÿª∑’Ë 1.3

—ßý§√“–ÀÏ

§«“¡∂’˥ȫ¬

«‘∏’ Direct

![]()

![]()

-238-

1.3.2 °“√ —ßý§√“–Àϧ«“¡∂’˥ȫ¬°“√§Ÿ≥ýÕ“µÏæÿµ

§«“¡∂’ËýÕ“µÏæÿµ¢Õßý§√◊ËÕß —ßý§√“–Àϧ«“¡∂’Ë∑’Ë· ¥ß„π√Ÿª∑’Ë 1.3 π—Èπ “¡“√∂π”¡“§Ÿ≥¥È«¬§Ë“ H ‚¥¬„™È«ß®√§Ÿ≥§«“¡∂’Ë∑’Ë¡’‰¥Õ–·°√¡°“√∑”ß“πµ“¡√Ÿª∑’Ë 1.4 ´÷Ëß®–∑”„Àȧ«“¡∂’Ë¢Õß —≠≠“≥ýÕ“µÏæÿµ¡’§Ë“¥—ßπ’È

fo

= N.(H.fR)

·µËý§√◊ËÕß —ßý§√“–Àϧ«“¡∂’˵“¡√Ÿª∑’Ë 1.4 ®–¡’¢ÈÕý ’¬Õ¬ŸË 2 ¢ÈÕ¥—ßπ’È

1) «ß®√§Ÿ≥§«“¡∂’Ë∑’Ëý√“„™È®–‰¡Ë¡’ª—≠À“·µËª√–°“√„¥ ∂È“„π√–∫∫¢Õßý√“π—Èπ¡’ý撬ߧ«“¡∂’Ëý¥’¬«∑’Ë∂Ÿ°§Ÿ≥ À√◊Õ §«“¡∂’Ë∑’Ë∂Ÿ°§Ÿ≥π—Èπ¡’°“√ýª≈’ˬπ·ª≈߉ª¡“ýæ’¬ßý≈Á°πÈÕ¬ý∑Ë“π—Èπ ·µË∂È“ý√“µÈÕß°“√§«“¡∂’Ë∑’Ë¡’§Ë“

¡“° Ê π—Èπý√“®–µÈÕß„™È«ß®√∑’Ë∑”„ÀÈ “¡“√∂§Ÿ≥§Ë“§«“¡∂’ËÕÕ°¡“‰¥Èլ˓ß∂Ÿ°µÈÕß·≈–«ß®√§Ÿ≥§«“¡∂’Ë

∑’Ë„™È®–µÈÕß¡’°“√®”°—¥·∫π¥Ï«‘¥∏Ïýæ◊ËÕ„Àȉ¥È™Ë«ß§«“¡∂’Ë∑’˵ÈÕß°“√ý∑Ë“π—Èπ

2) °“√ýª≈’ˬπ·ª≈ß∑“ߧ«“¡∂’Ëýæ’¬ßý≈Á°πÈÕ¬®“°¿“§ VCO ´÷Ëß®–∑”„Àȧ«“¡∂’Ë∑’˧Ÿ≥‰¥È¥È«¬ H ý°‘¥°“√ ýª≈’ˬπ·ª≈ß∑’Ë¡’§Ë“¡“°

X H LOW-PASS FILTER PHASE COMPARATOR

fR Fo

Fo = N(H.FR)

![]()

![]()

¸N![]()

![]()

-239-

1.3.4 °“√ —ßý§√“–Àϧ«“¡∂’˥ȫ¬°“√ýª≈’Ë¬π§«“¡∂’Ë(‚¥¬„™È¡‘°ý´Õ√Ï)

ý√“¡’«‘∏’°“√ 2 «‘∏’„π°“√ —ßý§√“–Àϧ«“¡∂’˥ȫ¬«‘∏’°“√ýª≈’Ë¬π§«“¡∂’˧◊Õ °“√ýª≈’Ë¬π§«“¡∂’Ë„ÀÈ Ÿß¢÷È𠵓¡√Ÿª∑’Ë 1.6 ·≈–°“√ýª≈’Ë¬π§«“¡∂’Ë„ÀÈ≈¥µË”≈ß µ“¡√Ÿª∑’Ë 1.7

®“°«ß®√„π√Ÿª∑’Ë 1.6 §«“¡∂’ËýÕ“µÏæÿµ fo∑’ˉ¥È®“°°“√ —ßý§√“–Àϧ«“¡∂’Ë®–∂Ÿ°ýª≈’Ë¬π§«“¡∂’Ë„ÀÈ¡’§Ë“ Ÿß¢÷Èπ§◊Õ

fo =

fL + NfR‚¥¬„™Èµ—«¡‘°ý´Õ√Ï ·≈–¿“§°”ý𑥧≈◊Ëπ —≠≠“≥§«“¡∂’Ë∑’Ë„™Èº≈÷°§«Õµ´Ï„π°“√ √È“ß —≠≠“≥§«“¡∂’Ë

fL

„π°√≥’¢Õß«‘∏’°“√π’È°Á¡’¢ÈÕ®”°—¥ý™Ëπý¥’¬«°—π°—∫«‘∏’°“√„πÀ—«¢ÈÕ∑’Ë 1.3.2 ´÷Ëß®”ýªÁπµÈÕß„™È«ß®√®Ÿπ∑’ËýÕ“µÏæÿµ ´÷Ëß∑”„ÀÈ«ß®√¡’§«“¡´—∫´ÈÕπ¡“°¬‘Ëߢ÷Èπ

¬‘Ë߉ª°«Ë“π—Èπ¿“§°”ýπ‘¥ —≠≠“≥∑ÈÕß∂‘Ëπ∑’Ë„™È®–‰¡Ë√«¡Õ¬ŸË„π«ß®√ PLL ´÷Ëß∑”„Àȧ˓§«“¡º‘¥æ≈“¥∑’Ëý°‘¥®“°¿“§°”ýπ‘¥ —≠≠“≥∑ÈÕß∂‘Ëπ∂Ÿ°·°È‰¢¥È«¬ PLL ‚¥¬Õ—µ‚π¡—µ‘∑”„Àȉ¡Ë®”ýªÁπµÈÕß«ß®√®Ÿπ∑’ËýÕ“µÏæÿµ ·µË¿“§ VCO π’È®–

√È“ß —≠≠“≥§«“¡∂’Ë‚¥¬µ√ß¡’§Ë“ý∑Ë“°—∫ fL + NfR

![]()

MIXER V C O LOW-PASS FILTER PHASE COMPARATOR

X

fR fo =

N.fR fo

= fL + NfR

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() fL

fL

¸

N![]()

-240-

1.3

ø—ß°Ï™—Ëπ∂Ë“¬‚Õπ·≈–°“√µÕ∫ πÕß∑√“πý™’¬πµÏ

°“√«‘ý§√“–ÀÏÀ“ø—ß°Ï™—Ëπ∂Ë“¬‚Õπ·≈–°“√µÕ∫ πÕß∑√“πý™’¬πµÏπ—Èπ¡’§«“¡ ”§—≠¡“° ”À√—∫°“√ÕÕ°·∫∫µ—« —ßý§√“–Àϧ«“¡∂’Ë

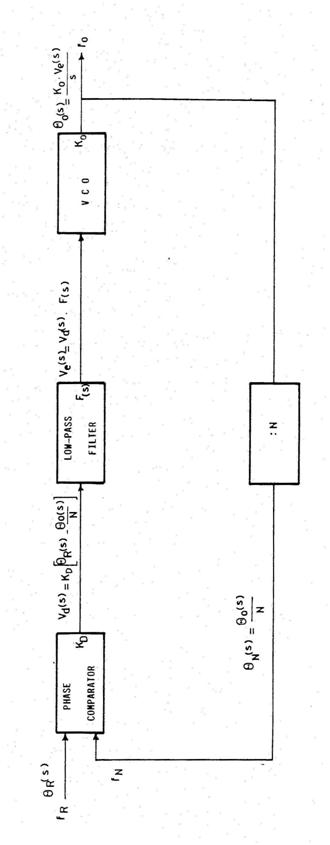

æ‘®“√≥“‰¥Õ–·°√¡„π√Ÿª∑’Ë 1.8 ´÷ËßýªÁπ‰¥Õ–·°√¡¢Õß°“√ —ßý§√“–Àϧ«“¡∂’Ë‚¥¬·µË≈–∫≈ÁÕ°π—Èπ®–¡’ø—ß°Ï™—Ëπ∂Ë“¬‚Õπ∫Õ°‰«È

—≠≠“≥ÕÈ“ßÕ‘ß∑’Ë¡’ýø qR·≈–∑’ËýÕ“µÏæÿµ¢Õß¿“§ VCO π—Èπ®–¡’ýø ýªÁπ qO

ýÕ“µÏæÿµ¢Õßµ—«ýª√’¬∫ý∑’¬∫ýø π—Èπ®–·ª√º—π‚¥¬µ√ßµËէ˓§«“¡·µ°µË“ß√–À«Ë“ßýø ¢ÕßÕ‘πæÿµ∑—Èß Õß·≈–Õ—µ√“°“√¢“¬ KD¥—ßπ’È

Vd

= KD( q

R - qO) = KD Dq

´÷Ëßý√“ “¡“√∂ªÈÕß°—𧫓¡º‘¥æ≈“¥∑’Ëý°‘¥®“°ýø ‰¥È‚¥¬°“√„™È«ß®√°√Õß —≠≠“≥§«“¡∂’˵˔ºË“πýæ◊ËÕ≈¥§Ë“§«“¡º‘¥æ≈“¥·≈–ªÈÕß°—π —≠≠“≥§«“¡∂’Ë Ÿß

∑”„ÀÈý√“‰¥È·√ߥ—π Vd

-241-

√Ÿª∑’Ë1.8

‰¥Õ–·°√¡µ—« —ßý§√“–Àϧ«“¡∂’Ë

-242-

ø—ß°Ï™—Ëπ∂Ë“¬‚Õπ¢Õß«ß®√°√Õß —≠≠“≥§◊Õ F(s)

§«“¡∂’Ë∑’ˉ¥È®“°¿“§ VCO π—Èπ®–¡’§Ë“·ª√º—πµ“¡·√ߥ—πýÕ“µÏæÿµ¢Õß«ß®√°√Õß —≠≠“≥ Ve

§«“¡∂’ËýÕ“µÏæÿµ®“°¿“§ VCO π—Èπ∂Ÿ°°”À𥂥¬·√ߥ—π Ve·≈–Õ—µ√“°“√¢¬“¬ Ko¥—ßπ’È

wo

= KO - Ve

®“°√Ÿª

q R(S) = ýø ¢Õß —≠≠“≥ÕÈ“ßÕ‘ß

qO(S) = ýø ¢Õß —≠≠“≥ýÕ“µÏæÿµ

Vd (S) = ·√ߥ—πýÕ“µÏæÿµ¢Õß¿“§ýª√’¬∫ý∑’¬∫ýø

F(S) = ø—ß°Ï™—Ëπ∂Ë“¬‚Õπ¢Õß«ß®√°√Õß —≠≠“≥

Ve(S) = ·√ߥ—π∑’Ëý°‘¥®“°§«“¡º‘¥æ≈“¥

KD = Õ—µ√“°“√¢¬“¬¢Õß¿“§ýª√’¬∫ý∑’¬∫ýø

(‚«≈µÏ/ý√ý¥’¬π)

KO = Õ—µ√“°“√¢¬“¬¢Õß VCO![]()

1/N = µ—«À“√¢Õßµ—«À“√§«“¡∂’Ë

ª°µ‘·≈È«§«“¡∂’Ë°Á§◊ÕÕπÿæ—π∏Ï¢Õßýø °“√∑”ß“π¢Õß¿“§ VCO π—Èπ “¡“√∂Õ∏‘∫“¬‰¥È¥È«¬§«“¡ —¡æ—π∏Ïπ’È¥—ßπ’È

dqo

= KO.Ve

![]() dt

dt

®“°°“√·ª≈ß≈“ª“´¢Õß ¡°“√¢È“ß∫ππ’Èý√“®–‰¥È

L(![]() ) = SqO(S)

= KO.Ve(S)

) = SqO(S)

= KO.Ve(S)

ý¡◊ËÕ

q O(S)

=![]()

-243-

π—ËπÀ¡“¬§«“¡«Ë“ýø ýÕ“µÏæÿµ¢Õß —≠≠“≥®“°¿“§ VCO π—Èπ·ª√º—π‚¥¬µ√ßµËÕº≈°“√Õ‘π∑√’ý°√µ¢Õß·√ߥ—π

§«∫§ÿ¡ Ve

‚¥¬°“√À“°“√·ª≈ß≈“ª“´¢Õß ¡°“√¢Õß√–∫∫ PLL ∑—ÈßÀ¡¥¥—ßπ’È

Vd(S)

= KD[qR(S)

- qN

(S)]

Ve(S)

= F(S).Vd(S)

qO(S)

= ![]()

ý¡◊ËÕ

wn

= ![]()

![]()

®“°π—Èπ„™Èµ—«°√Õß —≠≠“≥µ“¡√Ÿª∑’Ë 1.10 ´÷Ëß¡’ø—ß°Ï™—Ëπ∂Ë“¬¥Õπ¢Õßµ—«°√Õß —≠≠“≥π’È¥—ßπ’È

F(S)

=![]()

ý¡◊ËÕ

t1

= R1C

ý√“®–‰¥Èø—ß°Ï™—Ëπ∂Ë“¬‚Õπ¢Õßµ—« —ßý§√“–Àϧ«“¡∂’Ë¥—ßπ’È

2

![]()

H2 (S) = 2 2

ý¡◊ËÕ

wn

= ![]()

qN(S)

= ![]()

-244-

®“°§«“¡ —¡æ—π∏Ï°ËÕπÀπÈ“π’È ý√“ “¡“√∂À“ø—ß°Ï™—Ëπ∂Ë“¬‚Õπ H(S) ¢Õßµ—« —ßý§√“–Àϧ«“¡∂’ˉ¥È¥—ßπ’È

H(S)

=![]()

´÷Ëß®–ýÀÁπ«Ë“√Ÿª¢Õß ¡°“√π’È®–Õ¬ŸË„π√Ÿª¢Õßø—ß°Ï™—Ëπ∂Ë“¬‚Õπ H(s) ¢Õßµ—«°√Õß —≠≠“≥§«“¡∂’˵˔ºË“π

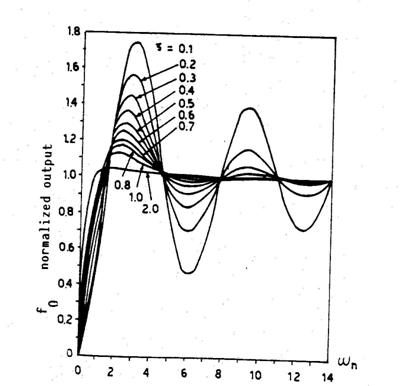

‚¥¬°“√„™Èµ—«°√Õß —≠≠“≥„π√Ÿª∑’Ë 1.9 ´÷Ëß¡’ø—ß°Ï™—Ëπ∂Ë“¬‚Õπ¥—ßπ’È

V

![]()

F(S) = V

ý¡◊ËÕ

t

= RC

¥—ßπ—Èπø—ß°Ï™—Ëπ∂Ë“¬‚Õπ¢Õßµ—«°√Õß —≠≠“≥§◊Õ

![]()

H1(S) = 2

∂È“ý√“„™È§Ë“ Damping factor t ·≈– Natural frequency wn·∑π§Ë“≈ß„π ¡°“√≈Ë“ ÿ¥ ý√“®–‰¥È

2

![]()

H(S) =

2

2

ý¡◊ËÕ

![]()

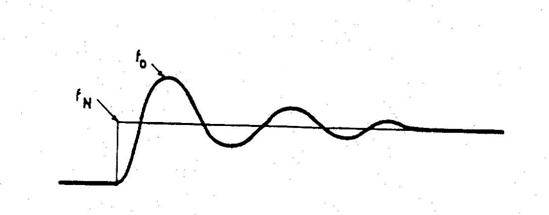

µËÕ‰ª∑”°“√æ‘®“√≥“∂÷ß ‘Ëß∑’Ëý°‘¥°—∫§«“¡∂’ËýÕ“µÏæÿµ¢Õßµ—« —ßý§√“–Àϧ«“¡∂’Ë fO ý¡◊ËÕ§«“¡∂’Ë fN ¡’§Ë“πÈÕ¬°«Ë“§«“¡∂’ËýÕ“µÏæÿµ∑’Ëýª≈’ˬπ·ª≈߉ªýπ◊ËÕß®“°°“√ýª≈’ˬπ·ª≈ßµ—«ª√–°Õ∫°“√À“√ N (µ“¡√Ÿª∑’Ë 1.11)

ýπ◊ËÕß®“°√–∫∫∑’Ë¡’ÕÕ√Ïý¥Õ√Ïý∑Ë“°—∫ 2 (®“°ø—ß°Ï™—Ëπ∂Ë“¬‚Õπ H(S)¢Õßµ—« —ßý§√“–Àϧ«“¡∂’Ë∑’ˉ¥Èæ∫«Ë“¡’ÕÕ√Ïý¥Õ√Ïý∑Ë“°—∫ 2 ) ®–∑”„ÀÈ —≠≠“≥ýÕ“µÏæÿµ¡’§Ë“µ“¡ —≠≠“≥Õ‘πæÿµ·µË®–¡’°“√ª√–«‘ßý«≈“·≈–°“√·°«Ëß√Õ∫ Ê —≠≠“≥ÕÈ“ßÕ‘ßý°‘¥¢÷Èπ

°“√ýª≈’ˬπ·ª≈ßլ˓ß√«¥ý√Á«¢Õß°√–∫«π°“√π’È®–¡’§Ë“¢÷ÈπÕ¬ŸË°—∫§Ë“ damping factor ¢Õßµ—«°√Õß —≠≠“≥ ´÷Ëß¡’§Ë“¢÷ÈπÕ¬ŸË°—∫Õÿª°√≥Ï∑’Ë„™È„π«ß®√°√Õß —≠≠“≥π—ËπýÕß

√Ÿª∑’Ë 1.12 · ¥ß„ÀÈ°“√µÕ∫ πÕß∑√“πý™’¬πµÏ∑’˺˓π°“√πÕ√¡Õ≈‰≈´Ï·≈È«¢Õß√–∫∫∑’Ë¡’µ—«°√Õß —≠≠“≥µ“¡«ß®√„π√Ÿª∑’Ë 1.9 ·≈–„π√Ÿª∑’Ë 1.13 ýªÁπ°“√µÕ∫ πÕß∑√“πý™’¬πµÏ¢Õß√–∫∫∑’Ë¡’µ—«°√Õß —≠≠“≥µ“¡«ß®√„π√Ÿª∑’Ë 1.10

-245-

®“°√Ÿª∑—Èß Õßý√“®–ýÀÁπ‰¥È«Ë“„π°√≥’À≈—ßπ—Èπ°√“ø®–¡’°“√ýª≈’ˬπ·ª≈ß∑’Ëý√Á«°«Ë“°√≥’·√°

π—Ëπ§◊Õ¡’°“√µÕ∫ πÕß∑’Ëý√Á«°«Ë“„π°√≥’·√°

![]()

![]()

![]()

![]()

![]()

![]()

![]() Vin Vout

Vin Vout

![]()

![]()

![]() C

C

![]()

√Ÿª∑’Ë 1.9 «ß®√ R-C ∑’Ë„™ÈýªÁπ«ß®√°√Õß —≠≠“≥

R1

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() Vin

Vout

Vin

Vout

![]() R2

R2

![]()

![]()

![]()

![]() C

C

![]()

√Ÿª∑’Ë 1.10 «ß®√ R-C ∑’Ë„™ÈýªÁπ«ß®√°√Õß —≠≠“≥

-246-

√Ÿª∑’Ë 1.11 °“√µÕ∫ πÕß∑√“πý™’¬πµÏ¢Õßµ—« —ßý§√“–Àϧ«“¡∂’Ë

√Ÿª∑’Ë 1.12

-247-

√Ÿª∑’Ë

1.13

√“¬≈–ýÕ’¬¥«ß®√

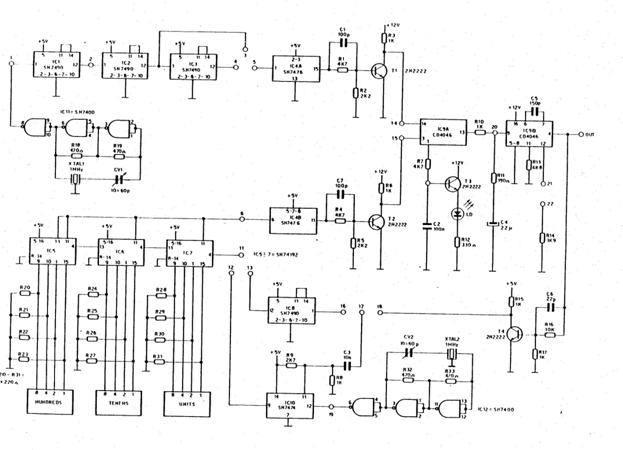

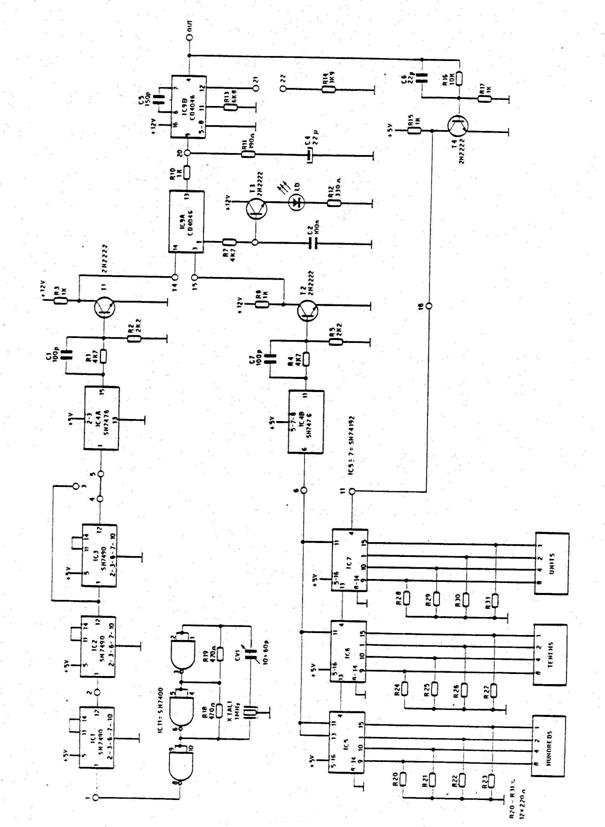

√Ÿª∑’Ë 2.1 · ¥ß‰¥Õ–·°√¡¢Õß«ß®√ ¡∫Ÿ√≥Ï¢Õß·ºß°“√∑¥≈Õß ´÷Ëߪ√–°Õ∫¥È«¬

-

µ—«ýª√’¬∫ý∑’¬∫ýø ·≈– VCO

-

Prescaler

-

µ—«À“√·∫∫‚ª√·°√¡‰¥È‚¥¬°“√ª√—∫‚√µ“√’Ë «‘µ™Ï

-

µ—«À“√·∫∫§Ë“§ß∑’Ë

-

ÕÕ ´‘≈ý≈ýµÕ√Ï·∫∫„™Èº≈÷°§«Õµ´Ï

-

¡‘°ý´Õ√Ï

- µ—«°√Õß —≠≠“≥§«“¡∂’˵˔ºË“π

-248-

-

„πÀ—«¢ÈÕ∂—¥‰ªý√“®–‰¥ÈÕ∏‘∫“¬∂÷ß√“¬≈–ýÕ’¬¥„π·µË≈– Ë«π¢Õß«ß®√¢Õßµ—« —ßý§√“–Àϧ«“¡∂’ËÀ≈“¬

Ê ·∫∫

√Ÿª∑’Ë

2.1 «ß®√

2.1 µ—« —ßý§√“–Àϧ«“¡∂’Ë·∫∫ Direct

‚¥¬°“√„™È«ß®√„π√Ÿª∑’Ë 2.1 ý√“ “¡“√∂ √È“ßµ—« —ßý§√“–Àϧ«“¡∂’Ë·∫∫ Direct ‰¥Èµ“¡«ß®√„π√Ÿª∑’Ë 2.2

´÷Ëßý√“®–„™È

-

ÕÕ ´‘≈ý≈ýµÕ√Ï·∫∫§«Õµ´Ï∑’Ë¡’µ—«À“√·∫∫§Ë“§ß∑’Ë

(IC11 ñ IC1-IC2 ñIC3 ñ IC4A)

-

µ—«ýª√’¬∫ý∑’¬∫ýø (IC9A)

-

µ—«°√Õß —≠≠“≥§«“¡∂’˵˔ºË“π(R10

ñR11 ñC4)

-

VCO(IC9B)

-

µ—«À“√·∫∫‚ª√·°√¡‰¥È(IC5-IC6-IC7)

µËÕ‰ª®–ýªÁπ Ë«πÕ∏‘∫“¬À≈—°°“√∑”ß“π¢Õß«ß®√„π·µË≈– Ë«π

-249-

2.1.1 ÕÕ ´‘≈ý≈ýµÕ√Ï·∫∫§«Õµ´Ï

ÕÕ ´‘≈ý≈ýµÕ√Ïπ’È®–„™Èý°∑ NAND 2 µ—« ‚¥¬¡’°“√ªÈÕπ°≈—∫ºË“πº≈÷°§«Õµ´Ï∑’Ë¡’§«“¡∂’Ë 1 MHz

µ—«ý°Á∫ª√–®ÿ·∫∫ª√—∫§Ë“‰¥È CV1 ∂Ÿ°„™È ”À√—∫ª√—∫§Ë“§«“¡∂’Ë„ÀÈ∂Ÿ°µÈÕß Ë«πý°∑µ—«∑’Ë “¡∑’Ëý™◊ËÕ¡µËÕ√–À«Ë“ßÕÕ ´‘≈ý≈ýµÕ√Ï°—∫«ß®√∑’Ëý™◊ËÕ¡µËÕ°—∫ÕÕ ´‘≈ý≈ýµÕ√Ïπ—Èπ®–∑”ÀπÈ“∑’ËýªÁπ∫—øýøÕ√Ï

∂È“ý√“µÈÕß°“√ √È“ß —≠≠“≥§«“¡∂’˵˔ (´÷Ëß∑”‰¥È¬“°„π°√≥’∑’Ë„™ÈÕÕ ´‘≈ý≈ýµÕ√Ï·∫∫º≈÷°§«Õµ´Ï„π°“√ √È“ß) “¡“√∂∑”‰¥È‚¥¬°“√µËÕ«ß®√À“√ 10 “¡«ß®√ (IC1 ñ IC2-IC3) ýæ◊ËÕÀ“√§«“¡∂’Ë¢Õß —≠≠“≥∑’ˉ¥Èý™Ëπ

1000

kHz/1000 = 1 kHz

´÷Ëß®–„™È«ß®√π—∫ ”À√—∫°“√À“√ Õß(‚¥¬„™Èø≈‘ªø≈Õª IC4 „π°“√ √È“ß) À“√Õ’°§√—Èß ”À√—∫ýÀµÿº≈π—Èπ®–Õ∏‘∫“¬„πÀ—«¢ÈÕ∑’Ë 2.1.4 ´÷Ëßý√“®–‰¥È§«“¡∂’ËÕÈ“ßÕ‘ß

fR

= 500 Hz

·≈–„™È∑√“π´’ ýµÕ√Ï T1ý™◊ËÕ¡µËÕ√–À«Ë“ß«ß®√

TTL(IC4) ·≈–«ß®√ CMOS(IC9A)

2.1.2 µ—«ýª√’¬∫ý∑’¬∫ýø ,µ—«· ¥ß°“√ ìlockî ·≈–µ—«°√Õß —≠≠“≥§«“¡∂’˵˔ºË“π

«ß®√√«¡ IC9(CD4046 ¥Ÿ√“¬≈–ýÕ’¬¥·≈–§ÿ≥ ¡∫—µ‘„π¿“§ºπ«°∑È“¬ý≈Ë¡)®–ª√–°Õ∫¥È«¬«ß®√ýª√’¬∫ý∑’¬∫ýø ,¿“§°”ýπ‘¥ —≠≠“≥¥È«¬ VCO ´÷Ëß®–‰¥ÈÕ∏‘∫“¬„πÀ—«¢ÈÕ∂—¥‰ª‚¥¬ CD4046 π—Èπ®–¡’µ—«ýª√’¬∫ý∑’¬∫ýø Õ¬ŸË 2 ·∫∫ ‚¥¬·∫∫·√°π—Èπ®–„™È«‘∏’°“√ Exclusive-OR Ë«πÕ’°·∫∫Àπ÷Ëßπ—Èπ®–„™È«‘∏’°“√ Edge-trigged(ý™Ëπ®–∑”ß“πý¡◊ËÕ¢Õ∫¢“¢÷Èπ¢Õß —≠≠“≥ý¢È“¡“∑’ËÕ‘πæÿµ)

„π°√≥’π’Èý√“®–„™Èµ—«ýª√’¬∫ý∑’¬∫ýø ·∫∫ ÿ¥∑È“¬ ´÷Ëß®–¡’√“¬≈–ýÕ’¬¥°“√∑”ß“π¥—ßπ’È

—≠≠“≥ÕÈ“ßÕ‘ß fR ®–ªÈÕπý¢È“∑’Ë¢“ 14 ·≈– —≠≠“≥ªÈÕπ°≈—∫∑’ˉ¥È®“°µ—«À“√·∫∫‚ª√·°√¡§Ë“‰¥È®–ªÈÕπý¢È“∑’Ë¢“ 13

µ—«ýª√’¬∫ý∑’¬∫ýø ®–∑”ß“πý¡◊ËÕ¢Õ∫¢Õß —≠≠“≥ª√“°Æ π—ËπÀ¡“¬§«“¡«Ë“„π√–À«Ë“ߥ‘«µ’ȉ´ý°‘È≈π—Èπ®–‰¡Ë¡’Õ–‰√ý°‘¥¢÷Èπ

∂È“ —≠≠“≥ÕÈ“ßÕ‘ß¡’ýø π”ÀπÈ“ —≠≠“≥®“°µ—«À“√·∫∫‚ª√·°√¡‰¥È®–∑”„ÀÈýÕ“µÏæÿµ¢Õßµ—«ýª√’¬∫ý∑’¬∫ýø

(¢“ 13) ¡’§Ë“ Ÿß„π™Ë«ß√–À«Ë“ßý«≈“¢ÕߢÕ∫¢Õß —≠≠“≥∑—Èß Õß(¥Ÿ√Ÿª∑’Ë 2.3)

∂È“ —≠≠“≥∑—Èß Õß¡’ýø ý¥’¬«°—π®–∑”„ÀÈýÕ“µÏæÿµ¢Õßµ—«ýª√’¬∫ý∑’¬∫ —≠≠“≥ý ¡◊Õπýª‘¥«ß®√ ·µË∂È“ —≠≠“≥ÕÈ“ßÕ‘ß¡’ýø ≈È“À≈—ß —≠≠“≥®“°µ—«À“√·∫∫‚ª√·°√¡§Ë“‰¥È ®–∑”„ÀÈýÕ“µÏæÿµ¢Õßµ—«ýª√’¬∫ý∑’¬∫ —≠≠“≥¡’§Ë“µË” ¥—ßπ—Èπ„π¢≥–∑’ËÕ¬ŸË„π ¿“æ ìno lockî ®–∑”„ÀÈý√“‰¥È —≠≠“≥æ—≈ Ï ≈—∫°—π√–À«Ë“ßæ—≈ Ï∫«°·≈–æ—≈ Ï≈∫ ·≈–®–∑”„ÀÈý°‘¥°“√ª√–®ÿ·≈–§“¬ª√–®ÿ°—∫µ—«ý°Á∫ª√–®ÿ¢Õßµ—«°√Õß —≠≠“≥ ´÷ËßýÕ“µÏæÿµ¢Õßµ—«°√Õß —≠≠“≥π’È®–‰¥È·√ߥ—π‰øøÈ“ýæ◊ËÕ𔉪¢—∫¿“§ VCO ®π°√–∑—Ëß√–∫∫Õ¬ŸË„π ¿“æ∑’Ë “¡“√∂ ìlockî ‰¥È

ý¡◊ËÕÕ¬ŸË„π ¿“æπ’È·≈È«ýÕ“µÏæÿµ¢Õßµ—«ýª√’¬∫ý∑’¬∫ýø —≠≠“≥®–ý ¡◊Õπýª‘¥«ß®√·≈–∑”„Àȵ—«ý°Á∫ª√–®ÿ√—°…“§Ë“·√ߥ—π¢Õßµ—«‰«È ”À√—∫§«∫§ÿ¡°“√∑”ß“π¿“§ VCO „ÀÈ∂Ÿ°µÈÕßµËÕ‰ª

-250-

√Ÿª

2.2

DIRECT

SYNTHESIZER

-251-

µ—«°√Õß —≠≠“≥®–¡’§ÿ≥ ¡∫—µ‘µ“¡¡“√µ√∞“π∑’ˉ¥ÈÕÕ°·∫∫‰«È®“°‚√ßß“πºŸÈº≈‘µµ—«‰Õ´’¥—ßπ’È

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() FR

(pin 14)

FR

(pin 14)

![]()

![]()

FN

(pin 3)

![]()

![]()

OUTPUT(pin 13)

![]()

![]()

![]()

![]()

![]() OF

OF

PHASE COMPARATOR low

![]()

![]()

![]()

![]() OUTPUT OF

OUTPUT OF

![]()

![]() LOW-PASS FILTER

LOW-PASS FILTER

OUTPUT OF high

LOCK INDICATOR

(pin 1)

![]()

![]() low

low

√Ÿª∑’Ë

2.3 √Ÿª§≈◊Ëπ¢Õßµ—«ýª√’¬∫ý∑’¬∫ýø

-252-

ý¡◊ËÕ

N §◊է˓¢Õßµ—«À“√„π Ë«π¢Õß°“√ªÈÕπ°≈—∫

fmax §◊Õ§«“¡∂’ËýÕ“µÏæÿµ Ÿß ÿ¥

f

= fmax - fmin

«ß®√√«¡®– Ëß —≠≠“≥∑’Ë¡’√–¥—∫·√ߥ—π Ÿß‰ª¬—ߢ“ 1 ý¡◊ËÕ√–∫∫ PLL “¡“√∂≈ÁÕ°§«“¡∂’ˉ¥È ·≈–®– Ëß —≠≠“≥∑’Ë¡’√–¥—∫·√ߥ—πµË”‰ª·∑π„π°√≥’°≈—∫°—π (¥Ÿ√Ÿª∑’Ë 2.2)

—≠≠“≥π’È®–∂Ÿ°°√Õß‚¥¬ R7 ñ C2 ·≈È«π”‰ª¢—∫∑√“π´’ ýµÕ√Ï T3 ·≈– LED ýæ◊ËÕ„™È„π°“√· ¥ß ¿“æ°“√∑”ß“π¢Õß PLL

2.1.3 ¿“§ VCO

„™È‰Õ´’ CD4046 ∑’Ë¡’«ß®√¢Õß¿“§ VCO Õ¬ŸË¿“¬„π

‚¥¬®–√—∫·√ߥ—π§«∫§ÿ¡∑’ˉ¥È®“°«ß®√°√Õß —≠≠“≥§«“¡∂’˵˔∑’Ë¢“ 20 ·≈– Ëß —≠≠“≥√Ÿª§≈◊Ëπ ’ËýÀ≈’ˬ¡‰ª¬—ßýÕ“µÏæÿµ∑’Ë¢“ 4

®“°√“¬≈–ýÕ’¬¥¢Õß‚√ßß“πºŸÈº≈‘µ∑”„ÀÈý√“∑√“∫‰¥È«Ë“§«“¡∂’Ë°÷Ëß°≈“ß §«“¡∂’Ë Ÿß ÿ¥·≈–§«“¡∂’˵˔ ÿ¥π—Èπ®–∂Ÿ°°”À𥂥¬µ—«ý°Á∫ª√–®ÿ∑’˵ËÕ√–À«Ë“ߢ“ 6 ·≈– 7 ·≈–µ—«µÈ“π∑“π∑’˵ËÕÕ¬ŸË√–À«Ë“ߢ“ 11 ·≈– 12 ´÷ËßýªÁπ‰ªµ“¡ ¡°“√¥—ßπ’È

![]()

![]()

![]()

-253-

™Ë«ß Capture range ·≈– Lock range ®–¡’§Ë“ý∑Ë“°—π ´÷Ëß®–¡’§Ë“¥—ßπ’È

fmax

- fmin

™Ë«ß Lock range §◊բ˫ߢÕߧ«“¡∂’Ë∑’Ë¡’§Ë“„°≈È fO ´÷Ëß PLL ¬—ß§ß “¡“√∂≈ÁÕ§§«“¡∂’Ë„ÀÈ„°≈Èý§’¬ß°—∫ —≠≠“≥

Õ‘πæÿµ‰¥È

™Ë«ß Capture range ª°µ‘®–¡’§Ë“µË”°«Ë“ Lock range ‚¥¬ýªÁπ§Ë“∑’Ë∫Õ°™Ë«ß¢Õߧ«“¡∂’Ë∑’Ë„°≈È fO ∑’Ë PLL “¡“√∂®–≈ÁÕ§§«“¡∂’ˉ¥È