|

|

|

วิชา ระบบสื่อสารแอนะลอก

หน่วยที่ 6 ชื่อหน่วย เฟสล็อกลูป จำนวน 6

คาบ

ใบงานที่

1 ชื่องาน การทำงานของ PLL จำนวน 1

คาบ

![]()

จุดประสงค์ทั่วไป

ศึกษาการทำงานของเฟสล็อกลูป (Phase Lock

จุดประสงค์เชิงพฤติกรรม

1.

อธิบายการทำงานของ PLL ได้

2.

คำนวณหา ความถี่สูงสุด และต่ำสุดของ Vco ได้

3.

คำนวณหา ความถี่ Look range และ Capture range ได้

เนื้อหา

1.1 หลักการทำงาน

เฟสล็อคลูป (Phase Locked

-

วงจรเปรียบเทียบเฟส

-

วงจรกรองสัญญาณความถี่ต่ำผ่าน

-

ภาคกำเนิดสัญญาณควบคุมแรงดัน (VCO)

วงจรเปรียบเทียบเฟสจะทำหน้าที่เปรียบเทียบเฟสระหว่างสัญญาณอินพุตที่เป็นแบบรายคาบกับสัญญาณที่ได้จากภาค VCO และให้เอาต์พุตของการเปรียบเทียบที่ได้แรงดัน

Vd แรงดันที่ได้นี้จะถูกกรองด้วยวงจรกรองสัญญาณความถี่ต่ำผ่านได้เป็นแรงดัน

Ve (เรียกว่า

"loop filter") แล้วป้อนให้กับภาค VCO ต่อไปแรงดัน Ve ที่ป้อนให้กับ VCO นั้นใช้สำหรับควบคุมความถี่เพื่อให้เฟสของสัญญาณอินพุตกับสัญญาณจากภาค

VCO นี้มีเฟสที่ตามกันหรือสามารถล็อคเฟสได้นั่นเอง

รูปที่ 1.1 ไดอะแกรมของ PLL

โดยปกติภาค VCO ของ PLL สามารถให้กำเนิดความถี่

fo ได้ถึงแม้ว่าเราจะไม่ทำการป้อนสัญญาณอินพุตเข้าไป

พารามิเตอร์ที่สำคัญที่สุดของ PLL คือ

-

-

รูปที่ 1.2 แสดงช่วงความถี่ Lock

Range และ

Capture Range ของ PLL ในรูปของแรงดันเทียบกับความถี่

ซึ่งความถี่ของสัญาณอินพุตนั้นสามารถเปลี่ยนแปลงได้ในช่วงกว้าง

ส่วนแกนตั้งนั้นแทนแรงดันควบคุม Ve ของภาค VCO พิจารณาที่ส่วนบนของวงจรในรูป

จะพบว่าถ้าเพิ่มค่า fi จะทำให้ PLL ไม่สามารถล็อคกับสัญญาณอินพุตได้ ถ้า fi ยังมีค่าไม่เท่ากับ

f2 ซึ่งเป็นค่าความถี่ต่ำสุดของ

Capture Range เมื่อ PLL สามารถล็อกความถี่ได้แล้วจะทำให้เกิดแรงดันลบขึ้นที่แรงดันควบคุม

Ve แรงดัน Ve

นี้จะมีค่าเปลี่ยนไปตามความถี่ที่เปลี่ยนไป

และจะมีค่าเป็นศูนย์เมื่อความถี่ fi = fo (ความถี่ free running) PLL

จะยังคงสามารถล็อกความถี่ต่อไปได้เรื่อยจนกระทั่ง

fi มีค่าเท่ากับ f4 ซึ่งเป็นค่าความถี่สูงสุดของ

Lock Range จะทำให้ PLL ไม่สามารถล็อกความถี่ของสัญญาณอินพุตได้ และแรงดัน Ve จะมีค่าเป็น 0

ดังนั้น

Dfc = f3

- f2

ส่วน

DfL = f4

- f1

+

![]()

![]()

FREQUENCY fi f2

f4 f0

LOCK

-

DfL

+

FREQUENCY fi f0 f3 f1 ve

-

รูปที่ 1.2 คุณสมบัติของ PLL ระหว่างความถี่เทียบกับแรงดัน

-197-

1.2

ออสซิลเลเตอร์ที่ควบุคมด้วยแรงดัน (VCO)

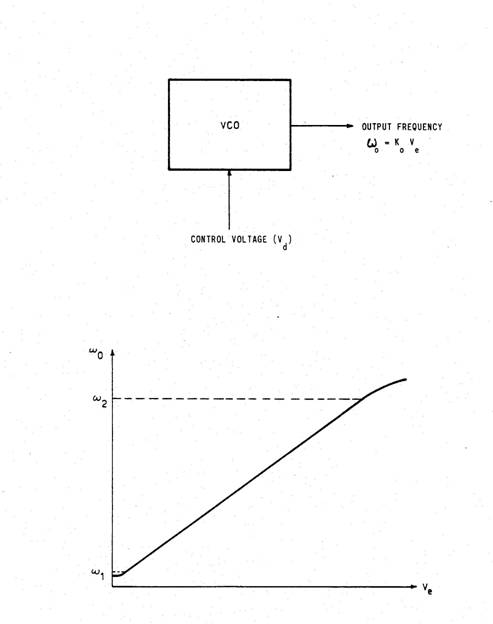

ภาค VCO

คือ ภาคกำเนิดสัญญาณที่มีความถี่ของสัญญาณแปรผันตามขนาดของแรงดันควบคุมด้านอินพุตตามรูปที่

1.3

คุณสมบัติที่สำคัญที่สุดของ

VCO คือ

-

Frequency range คือ

ช่วงความถี่ของสัญญาณที่ภาค VCO นี้สามารถสร้างขึ้นมาได้

-

Linearity คือ

ความเป็นเชิงเส้นเมื่อเทียบกันระหว่างความถี่ของสัญญาณเอาต์พุตต่อแรงดันควบคุม

ในรูปที่ 1.3 b นั้นจะแสดงคุณลักษณะของ VCO (ซีงจะมีความเป็นเชิงเส้นในช่วงความถี่ w1 ถึง w2 )

-

conversion gain คือ

อัตราส่วนระหว่างความถี่ของสัญญาณเอาต์พุตต่อแรงดันควบคุมอินพุต

มีค่าดังนี้

Ko = wo/Ve หน่วยเป็น rad/sec.volt

ภาค VCO นั้นสามารถสร้างจากวงจรอิเล็กทรอนิกส์ได้ เช่น

วงจรที่สร้างจากอุปกรณ์แบบดีสครีต,

วงจรรวมหรือไอซี, วงจรที่สร้างจาก LC,

RC, มัลติไวรเบรเตอร์ และอื่น ๆ ส่วน VCO ในชุดทดลองนี้จะใช้ไอซีเบอร์

uA565 มาสร้าง

-198-

รูปที่ 1.3

a)

ไดอะแกรมการทำงานของ

VCO

b)

คุณสมบัติการทำงานของ

VCO

1.3

วงจรเปรียบเทียบเฟส (Phase Comparator)

วงจรเปรียบเทียบเฟสจะทำหน้าที่เปรียบเทียบเฟสของสัญญาณอินพุต

2 สัญญาณแล้วให้เอาต์พุตเป็นแรงดันเฉลี่ยที่มีค่าแปรผันโดยตรงต่อค่าความแตกต่างระหว่างเฟสของสัญญาณอินพุตทั้งสอง

(ดูรูปที่ 1.4) วงจร

-199-

เปรียบเทียบเฟสสามารถสร้างได้จากวงจรดิจิตอลหรืออนาล็อกก็ได้ โดยถ้าใช้วงจรดิจิตอลนั้นก็มักจะใช้เกทแบบ

exclusive-or หรือ edge-triggered แต่ถ้าเป็นวงจรอนาล็อกก็จะใช้วงจรคูณแทน

สำหรับวิธีอื่น ๆ นอกเหนือจากนี้สามารถหาอ่านได้จากหนังสือหรือคู่มืออื่น ๆ

อย่างไรก็ตามสิ่งที่เราควรคำนึงถึงมากที่สุดคือประสิทธิภาพในการทำงานมากกว่าเทคนิคในการสร้าง

คุณสมบัติหลักคือ conversion gain

of the phase comparator ที่กำหนดให้มีค่าดังนี้

KD

= Vd/wDo หน่วยเป็น V/rad

เมื่อ

Vd คือ แรงดันเฉลี่ยเอาต์พุตของวงจรเปรียบเทียบ

มีหน่วยเป็นโวลต์

KD

คือ conversion gain มีหน่วยเป็น V/rad

Do คือ ค่าความต่างเฟสระหว่างสัญญาณอินพุตทั้งสอง

มีหน่วยเป็น rad

ในการคำนวณหาฟังก์ชั่นการถ่ายโอน (Transfer Function) นั้นจะได้กล่างถึงในภายหลัง

ซึ่งในวงจรเปรียบเทียบเฟสนี้จะแทนด้วย conversion gain KD

fo fi

ve

รูปที่ 1.4 ไดอะแกรมของวงจรเปรียบเทียบเฟส

แรงดัน Ve จะมีค่าแปรผันโดยตรงต่อค่าความต่างเฟสระหว่าง

fi และ fo

ระบบ PLL จะใช้ตัวกรองสัญญาณความถี่ต่ำผ่านต่อคาสเคดกับวงจรเปรียบเทียบเฟส

เพื่อทำหน้าที่สองประการดังนี้

-

กำจัดองค์ประกอบของสัญญาณเอาต์พุตจากวงจรเปรียบเทียบสัญญาณที่มีค่าความถี่สูงออกไป

และให้เอาต์พุตออกมาเป็นสัญญาณที่มีความต่อเนื่อง

-

เป็นส่วนการทำงานหลักที่ใช้ในการหาฟังก์ชั่นการถ่ายโอน

Capture

range และ Lock range ของ PLL

-200-

ตัวกรองสัญญาณความถี่ต่ำผ่านนั้นจะปรกอบขึ้นมาจากวงจรRC หรืออาจจะสร้างจากอุปกรณ์ประเภทแอกตีฟ (ตัวกรองสัญญาณแบบแอกตีฟ)

1.5 ฟังก์ชั่นการถ่ายโอนของ PLL

รูปที่ 1.5 แสดงไดอะแกรมของ

PLL

8i Ve = F(s)vd Vd = KD(qi-qo)

![]()

FILTER![]()

![]()

![]()

![]()

รูปที่ 1.5 ไดอะแกรมของ PLL

สัญญาณอินพุตที่มีเฟส 0i และเอาต์พุตของ

VCO จะมีเฟส 0o

เอาต์พุตของวงจรเปรียบเทียบเฟสนั้นจะมีค่าแปรผันโดยตรงต่อค่าความต่างเฟสระหว่างอินพุตทั้งสองคูณด้วยอัตราขยาย

KD

ดังนี้

Vd = KD (0i

- 0o) = KDD0

แรงดัน Vd

ที่ได้จะถูกป้อนผ่านตัวกรองสัญญาณความถี่ต่ำผ่านเพื่อกำจัดองค์ประกอบของสัญญาณที่มีความถี่สูงและสัญญาณรบกวนออกไป

ฟังก์ชั่นการถ่ายโอนของตัวกรองสัญญาณคือ F(s)

ภาค VCO

จะถูกควบคุมการผลิตสัญญาณด้วยแรงดันที่ได้มาจากตัวกรองสัญญาณ Ve ความถี่ของ

-201-

สัญญาณจาก VCO จะถูกกำหนดจากแรงดัน

Ve และ อัตราการขยาย Ko ดังนี้

wo = Ko . Ve

ความถี่ของสัญญาณ VCO ก็คืออัตราการเปลี่ยนเฟสของสัญญาณนั่นเอง

ดังนั้นเราจะได้

![]() d0o = Ko.Ve

d0o = Ko.Ve

dt

จาก

d0o

dt

![]()

![]() L

= s0o(s)

= Ko.Ve

L

= s0o(s)

= Ko.Ve

เพราะฉะนั้น

S

![]() 0o(s)

= KoVe(s)

0o(s)

= KoVe(s)

อินทรีเกรตของแรงดันควบคุม Ve

โดยการหา

Vd(s) = KD[0i(s)

- 0o(s)]

Ve(s) = F(s) . Vd(s)

S

![]() 0o(s)

= KoVe(s)

0o(s)

= KoVe(s)

เมื่อรวมความสัมพันธ์ทั้งหมดเข้าด้วยกัน

จะทำให้เราได้ฟังก์ชั่นการถ่ายโอนของระบบ PLL ดังนี้

H(s)

=

![]()

![]() =

=

จะเห็นได้ว่า ฟังก์ชั่นนี้มีคุณสมบัติที่ขึ้นอยู่กับฟังก์ชั่นการถ่ายโอนของตัวกรองสัญญาร

F(s)

รูปที่ 1.6 แสดงวงจรกรองสัญญาณที่ใช้ RC และมีฟังก์ชั่นการถ่ายโอนดังนี้

![]()

![]()

F(s) =

=

-202-

เมื่อ t = RC ในกรณีนี้เราจะได้ฟังก์ชั่นการถ่ายโอนของ

PLL ดังนี้

![]()

H(s) = 2

S2 + 2zwKns + wns

![]() w2n

w2n

![]()

![]()

![]()

เมื่อ wn =

และ z =

ซึ่ง z คือ damping

factor และ w คือ natural frequency

ค่า Capture range และ Lock range เป็นพารามิเตอร์ที่ต้องพิจารณาเป็นพิเศษในระบบ PLL ซึ่งเราสามารถหาค่าทั้งสองนี้ได้จากฟังก์ชั่นการถ่ายโอนดังนี้

![]()

Lock

range fd »

Hz

สำหรับ Capture range นั้นจะมีคุณสมบัติขึ้นอยู่กับคุณสมบัติของตัวกรองสัญญาณด้วย สำหรับในกรณีนี้เราจะได้

![]()

Capture

range fc »

Hz

R

![]()

![]()

![]() R

R

![]()

![]()

![]()

![]()

รูปที่ 1.6

อะไรจะเกิดขึ้นกับความถี่ของสัญญาณเอาต์พุต

fo ของ

PLL เมื่อความถี่ของสัญญาณอินพุต fi มีการเปลี่ยนแปลงทันทีทันใด

(ดูรูปที่ 1.7)

-203-

จาก H(s) ที่ได้จะเห็นว่าระบบ PLL นั้นเป็นระบบที่มีออร์เดอร์เป็น 2 นั่นหมายความว่าเอาต์พุตจะมีการเปลี่ยนแปลงตามอินพุต

แต่แกว่งไปมารอบจุดที่ต้องการระยะเวลานี้คือมีการหน่วงเวลาออกไป

ความเร็วของกระบวนการนี้จะขึ้นอยู่กับค่า damping

factor z ของระบบ

และค่านี้ก็จะขึ้นอยู่กับคุณลักษณะของตัวกรองสัญญาณนั่นเอง

รูปที่ 1.7 การตอบสนองทรานเชียนต์ของระบบ PLL

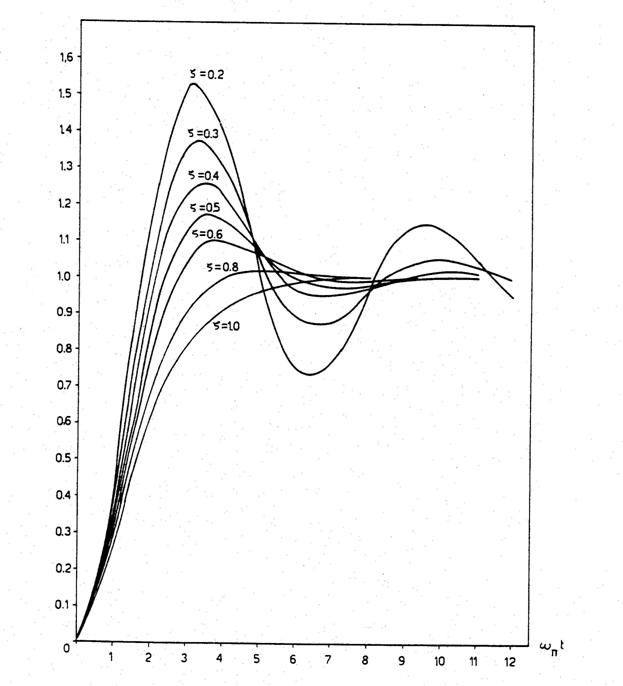

รูปที่ 1.8 แสดงดารตอบสนองต่อทรานเชียนต์ของระบบ PLL เมื่อ damping factor มีค่าต่าง

ๆ กัน ซึ่งจะเห็นว่าถ้า z

ยิ่งมีค่าลดลงเท่าใด

ก็จะยิ่งทำให้เกิดการแกว่งมากขึ้นเท่านั้น

-204-

รูปที่ 1.8 การตอบสนองทรานเชียนต์

-205-

เครื่องมือและอุปกรณ์

1.

แหล่งจ่ายไฟ ±

12 Vdc 1 ชุด

2.

ชุดกำเนิดสัญญาณ AM/FM ความถี่ต่ำ 1 ชุด

3.

ออสซิลโลสโคป 1 เครื่อง

4.

มิเตอร์วัดความถี่ 1 เครื่อง

5.

แผงทดลอง L05 1 ชุด

6.

สายต่อวงจร 30

เส้น

ลำดับการทดลอง

คุณลักษณะของ VCO

1.

คำนวณหาความถี่กลางของ VCO จากสมการต่อไปนี้

![]()

¦.

=

ในแผงทดลองนี้

ใช้ C2 =

2.2 nF และ RV1 จะประกอบด้วยตัวต้านทาน 1KW ต่ออนุกรมกับ

ทริมเมอร์ 4.7 KW

จากค่าดังกล่าว

สามารถหาค่าความถี่สูงสุด ¦max และความถี่ต่ำ ¦min ของ VCO ได้ดังนี้

![]()

@ 130 KHz

¦max -9

3

@ 23 KHz

![]()

¦max -9

3

2.

ต่อจุด 4 เข้ากับ 5

3.

ใช้มิเตอร์วัดความถี่ที่จุด 3 โดยหมุน RV1 เพื่อตรวจดูว่าความถี่ที่วัดได้มีค่าอยู่ระหว่าง 20KHz ถึง 130KHz

4.

วัดและบันทึกรูปคลื่นสัญญาณที่จุด 3 ด้วยออสซิลโลสโคป

5.

ถอดสายออกจากจุด 4 และ

5 และป้อนแรงดันไฟดี.ซี. ระหว่าง 7-10 V เข้าที่จุด 4 สังเกตความถี่ของสัญญาณมีการเปลี่ยนแปลงหรือไม่………………….

การคำนวณหาอัตราส่วนขยาย

K.

ของ VCO

6.

ต่อจุด 4 และ 5 เข้าด้วยกัน

และป้อนไฟเลี้ยงวงจร

7.

ต่อมิเตอร์วัดความถี่ที่จุด 3 และ

ปรับ RV1 ให้ความถี่ที่วัดได้มีค่าต่ำสุด

8.

ป้อนแรงดันไฟตรงขนาด 0-10 V. เข้าที่จุด 7 โดยปรับแรงดันทีละ 1 V.

-

วงจรเปรียบเทียบเฟส

เอาต์พุตของวงจรเปรียบเทียบเฟสของไอซี

uA565 ไม่สามารถวัดออกมาได้โดยตรง

แต่เราสามารถวัดเอาต์พุตของตัวกรองสัญญาณได้ที่จุด 7 แต่เราก็สามารถตรวจสอบการทำงานของวงจรเปรียบเทียบเฟสได้โดยมีขั้นตอนดังนี้

1)

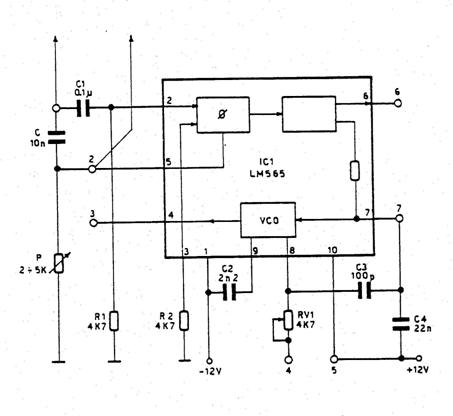

สร้างวงจรตามรูปที่ 3.2 เมื่อ P คือโพเทนชิโอมิเตอร์ที่มีค่าระหว่าง 2 kW ถึง 5 kW และ

C คือตัวเก็บประจุที่มีค่า 10nF

-208-

รูปที่ 3.2

2)

ใช้ออสซิลโลสโคปแบบ dual trace วัดที่จุด 1 และ 2 และใช้โวลต์มิเตอร์วัดที่จุด

7

3)

ป้อนสัญญาณรูปคลื่นซายน์ที่มีความถี่ประมาณ

50 kHz

และมีขนาดประมาณ 500 mVpp ที่อินพุตจุด 1

4)

ตรวจดูความต่างเฟสระหว่างสัญญาณที่วัดได้ที่จุด

1 และ 2 ในขณะเดียวกันค่อย ๆ ปรับโพเทนชิโอมิเตอร์

5)

ตรวจดูว่าแรงดันที่วัดได้ที่จุด 7 มีการเปลี่ยนแปลงหรือไม่เมื่อค่าความแตกต่างระหว่างเฟสของสัญญาณรูปคลื่นซายน์ทั้งสองที่วัดได้ที่จุด

1 และ 2 เปลี่ยนไป

-

Lock

range Capture range ของ PLL

Lock range fL และ Capture range fC มีค่าดังนี้

![]()

fL

»

fC »

3

-209-

เมื่อ

fo คือ ความถี่กลางของ VCO

Vc คือ แรงดันที่จ่ายให้วงจร (ในกรณีนี้คือ 24 V)

3.6

x 103

คือ

ความต้านทานขนาด 3.6 kW ซึ่งเป็นค่าความต้านทานภายในของไอซีในส่วน

ของตัวกรองสัญญาณ

C4 คือ ตัวเก็บประจุมีค่า 22nF

การวัดและตรวจสอบค่า Lock range นั้นทำได้ตามขั้นตอนดังนี้

1)

เชื่อมต่อจัมเปอร์

2-3 และ 4-5

2)

ป้อนไฟเลี้ยงให้วงจร

3)

ต่อมิเตอร์วัดความถี่ที่จุด 3 และปรับ

RV1 จนวัดความถี่ได้ 40 kHz

4)

วัดค่า fL และ fC

5)

ต่อออสซิลโลสโคปวัดสัญญาณที่จุด 3

6)

ป้อนสัญญาณรูปคลื่นซายน์ความถี่ประมาณ

40 kHz และมีขนาด 500 mVpp ที่จุด 1

7)

ปรับความถี่ของสัญญาณอินพุตและตรวจสอบความถี่ของสัญญาณที่ได้จาก VCO ที่จุด 3 ว่าสามารถล็อกกับความถี่ของสัญญาณอินพุตได้หรือไม่

ซึ่งควรจะมีค่าความถี่ระหว่าง

27 kHz ถึง

53 kHz

8)

สามารถล็อกความถี่นี้ได้

และ

VCO จะสร้างสัญญาณที่มีความถี่กลางออกมาจากนั้นปรับความถี่ของสัญญาณอินพุตให้มีค่าระหว่าง

34 kHz และ 46 kHz เพื่อให้ PLL

สามารถล็อกได้อีกครั้ง

ซึ่งช่วงความถี่นี้เป็น Capture

range และมีค่าน้อยกว่า Lock range

9)

ปรับค่า RV1 ให้ได้ความถี่ fo ประมาณ 60 kHz

10)

ต่อตัวเก็บประจุขนาด 50 nF ขนานกับ C4 (ระหว่างจุด

5 และ 7) และตรวจดูว่า Capture

range มีการเปลี่ยนแปลงหรือไม่

11)

ต่อโวลต์มิเตอร์หรือออสซิลโลสโคปวัดที่จุด 7 (เอาต์พุตของตัวกรองสัญญาณ)

ตรวจดูว่าระดับแรงดันมีค่าลดลงเมื่อความถี่ของสัญญาณอินพุตมีค่าเพิ่มขึ้น

ซึ่งระดับแรงดันนี้จะไปควบคุมการสร้างสัญญาณของภาค VCO